大話集成電路71 EDA工具——芯片軟件設(shè)計(jì)的利器

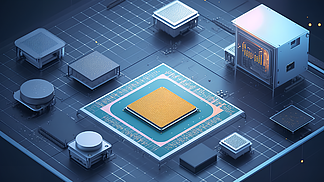

在當(dāng)今這個(gè)信息爆炸的時(shí)代,芯片作為電子產(chǎn)品的“心臟”,其重要性不言而喻。從智能手機(jī)到超級(jí)計(jì)算機(jī),從家用電器到航天器,幾乎每一個(gè)現(xiàn)代設(shè)備都離不開芯片的驅(qū)動(dòng)。你是否曾想過,這些集成了數(shù)十億甚至數(shù)百億個(gè)晶體管的復(fù)雜電路,是如何被設(shè)計(jì)出來的呢?答案就在于一套被稱為“電子設(shè)計(jì)自動(dòng)化”(EDA)的強(qiáng)大軟件工具。

EDA工具,堪稱集成電路設(shè)計(jì)領(lǐng)域的“瑞士軍刀”。在芯片設(shè)計(jì)的每一個(gè)環(huán)節(jié),從最初的構(gòu)思到最終的制造,EDA工具都扮演著不可或缺的角色。我們可以將其比作建筑師手中的CAD軟件,沒有它,設(shè)計(jì)一座摩天大樓幾乎是不可能完成的任務(wù);同樣,沒有EDA工具,設(shè)計(jì)一顆先進(jìn)的芯片也無異于天方夜譚。

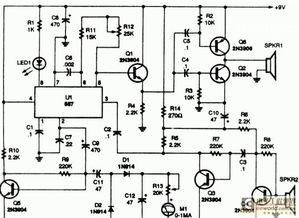

讓我們從芯片設(shè)計(jì)的起點(diǎn)——邏輯設(shè)計(jì)說起。工程師們使用硬件描述語言(如Verilog或VHDL)來“描述”芯片需要實(shí)現(xiàn)的功能。這就像用一門特殊的編程語言來編寫芯片的“行為規(guī)范”。EDA工具中的“邏輯綜合”工具會(huì)將這種高級(jí)描述,轉(zhuǎn)換成一連串的門級(jí)電路網(wǎng)表,即由基本邏輯門(如與門、或門、非門)構(gòu)成的連接圖。這個(gè)過程充滿了優(yōu)化,目標(biāo)是在滿足功能的前提下,追求更小的面積、更低的功耗和更快的速度。

接下來進(jìn)入物理設(shè)計(jì)階段,這是EDA工具大顯身手的核心戰(zhàn)場(chǎng)。想象一下,要把數(shù)億個(gè)邏輯門和它們之間的連線,合理地“擺放”在一塊指甲蓋大小的硅片上,并確保所有信號(hào)能夠正確、及時(shí)地傳遞,同時(shí)還要處理功耗、散熱、制造工藝限制等一系列棘手問題。這其中的復(fù)雜程度,遠(yuǎn)超任何人類手工所能及。

- 布局規(guī)劃:工具首先對(duì)芯片進(jìn)行宏觀規(guī)劃,劃分不同功能模塊(如CPU核心、內(nèi)存控制器等)的大致區(qū)域。

- 布局:將一個(gè)個(gè)具體的標(biāo)準(zhǔn)單元(實(shí)現(xiàn)基本邏輯功能的預(yù)制電路塊)精確地放置在芯片版圖上。

- 布線:在單元之間,根據(jù)邏輯連接關(guān)系,鋪設(shè)數(shù)百萬甚至數(shù)十億條金屬導(dǎo)線。這就像在一個(gè)極度擁擠的城市里規(guī)劃所有道路,且不能有任何短路或斷路。現(xiàn)代EDA的布線算法極其智能,能自動(dòng)繞開障礙,優(yōu)化路徑。

- 時(shí)序分析與優(yōu)化:確保信號(hào)從一點(diǎn)傳到另一點(diǎn)的時(shí)間滿足設(shè)計(jì)要求。芯片時(shí)鐘頻率高達(dá)數(shù)GHz,任何微小的延遲差錯(cuò)都可能導(dǎo)致功能失敗。工具會(huì)反復(fù)迭代,調(diào)整布局布線,直至滿足所有時(shí)序約束。

- 物理驗(yàn)證:在交付制造前,進(jìn)行一系列嚴(yán)格的“體檢”,檢查版圖是否符合制造工藝的設(shè)計(jì)規(guī)則(DRC),電路連接是否與原始設(shè)計(jì)一致(LVS),以及是否存在信號(hào)完整性、電遷移等可靠性問題。

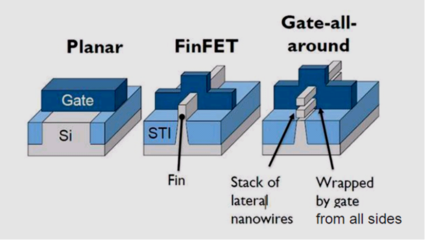

除了這些核心步驟,EDA工具還覆蓋了模擬電路設(shè)計(jì)、芯片封裝設(shè)計(jì)、功耗分析、可測(cè)試性設(shè)計(jì)等方方面面。隨著工藝進(jìn)入納米乃至更先進(jìn)的節(jié)點(diǎn),設(shè)計(jì)復(fù)雜度呈指數(shù)級(jí)增長(zhǎng),EDA工具也日益集成人工智能和機(jī)器學(xué)習(xí)技術(shù),以幫助工程師應(yīng)對(duì)“設(shè)計(jì)圍墻”的挑戰(zhàn)。

可以說,EDA是連接芯片創(chuàng)意與硅片實(shí)物的橋梁。沒有這套強(qiáng)大的軟件利器,我們手中那些功能強(qiáng)大的芯片將永遠(yuǎn)停留在圖紙階段。它不僅是設(shè)計(jì)工具,更是創(chuàng)新加速器,持續(xù)推動(dòng)著集成電路產(chǎn)業(yè)向著更高性能、更低功耗、更小尺寸的方向邁進(jìn)。因此,當(dāng)我們?yōu)樾乱淮酒耐黄贫鴼g呼時(shí),也請(qǐng)不要忘記背后那些默默無聞的EDA工具及其開發(fā)者們,他們正是芯片軟件設(shè)計(jì)王國(guó)里真正的“鑄劍大師”。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.iwgw.cn/product/50.html

更新時(shí)間:2026-04-18 04:21:13